#### **Fundamentals of Switched-Mode Power Converter Design**

#### Hoi Lee

#### Professor Department of Electrical and Computer Engineering The University of Texas at Dallas hoilee@utdallas.edu

#### Feb. 11, 2018

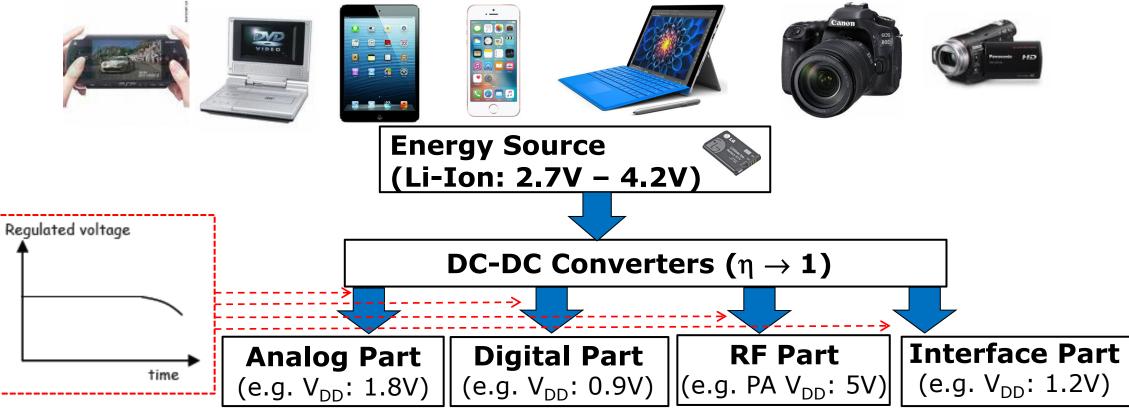

# Why DC-DC Converters?

#### Battery-Operated Portable Electronic Gadgets

□ Battery voltage is time-varying.

□ DC-DC converters are part of power management to provide regulated voltages.

## Types of DC-DC Converters

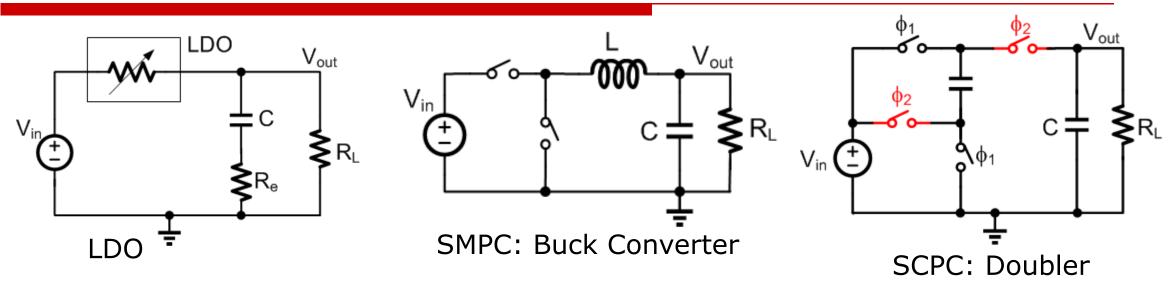

#### Low Dropout Regulator (LDO)

□ Continuous-time system with a single power transistor

Switched-Mode Power Converter (SMPC)

□ Sampled-data system using inductor for energy storage

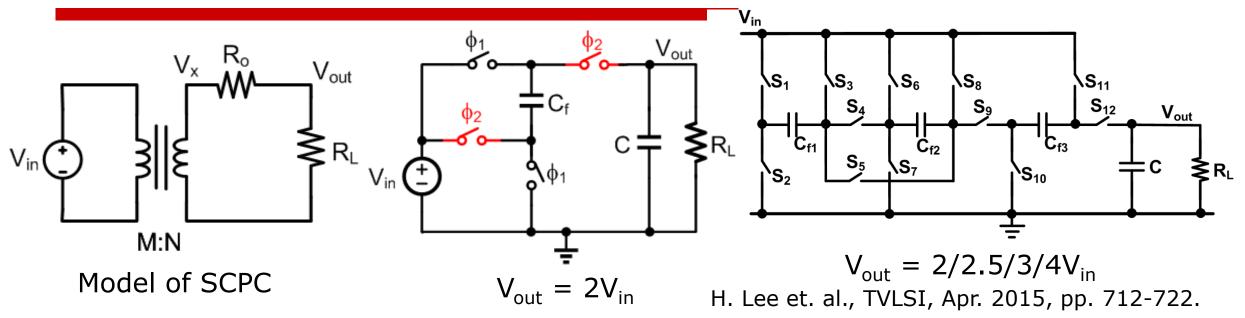

#### Switched-Capacitor Power Converter (SCPC)

□ Sampled-data system using capacitor for energy storage

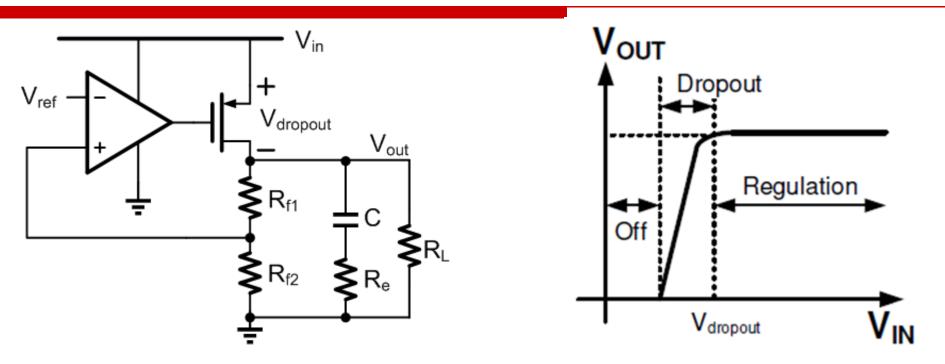

## Low Dropout Regulator

- $\Box$  Based on the LDO structure, V<sub>out</sub> is always smaller than V<sub>in</sub>.

- □ As input current  $\approx$  load current,  $\eta$  approximately equals  $V_{out}/V_{in}$  (=1-( $V_{dropout}/V_{in}$ )).

- In practice, Power pMOS can reduce V<sub>dropout</sub> to about 0.1V 0.2V and is more commonly used than nMOS counterpart for maximizing η.

- $\Box$  Power FET does not switch during operation, so V<sub>out</sub> is low noise.

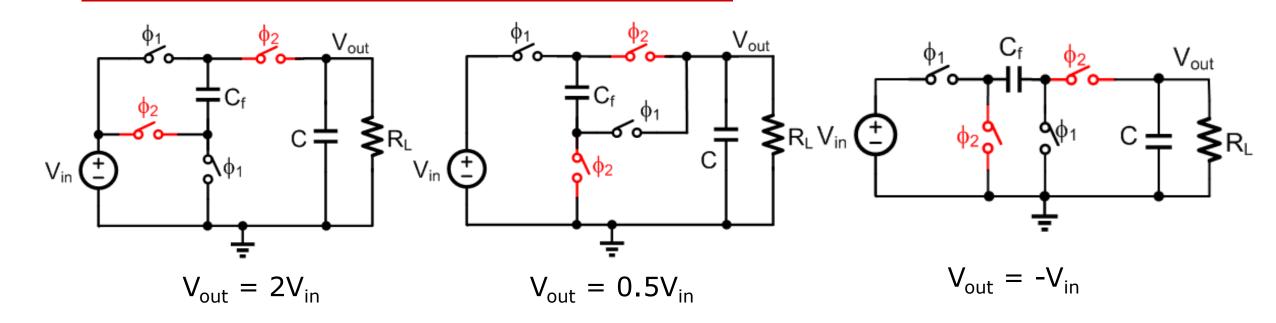

#### Switched-Capacitor Power Converters (1)

- By changing connections of switches and capacitors, different conversion ratios between V<sub>in</sub> and V<sub>out</sub> (step-up, step-down or inverting) can be realized.

- $\Box$  Flying capacitor C<sub>f</sub> is used for temporary energy storage.

- □  $V_{out}$  relates to  $V_{in}$  with a fixed conversion ratio via two complimentary clock phases  $\phi_1$  and  $\phi_2$ .

#### Switched-Capacitor Power Converters (2)

- □  $V_{out} = (N/M) \cdot R_L / (R_L + R_O) \cdot V_{in}$ , so  $V_{out}$  can be regulated by adjusting output resistance  $R_O$  of the power stage; where N/M is the conversion ratio.

- $\Box \quad \text{Ideal } \eta = (V_{\text{out}} \cdot I_{\text{out}}) / V_{\text{in}} \cdot I_{\text{in}} = (V_{\text{out}} / V_x) \cdot (V_x / V_{\text{in}}) \cdot (I_{\text{out}} / I_{\text{in}}) = V_{\text{out}} / V_x \text{ (i.e. } \eta \text{ of LDO).}$

- $\Box$  Lossless V<sub>out</sub> regulation is to change N/M when V<sub>in</sub> varies.

- Numbers of flying capacitors and switches however grow rapidly when the resolution of input-output conversion ratio increases.

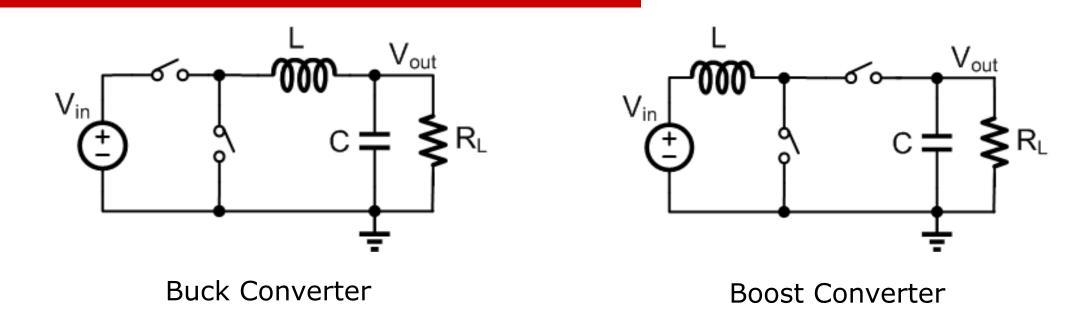

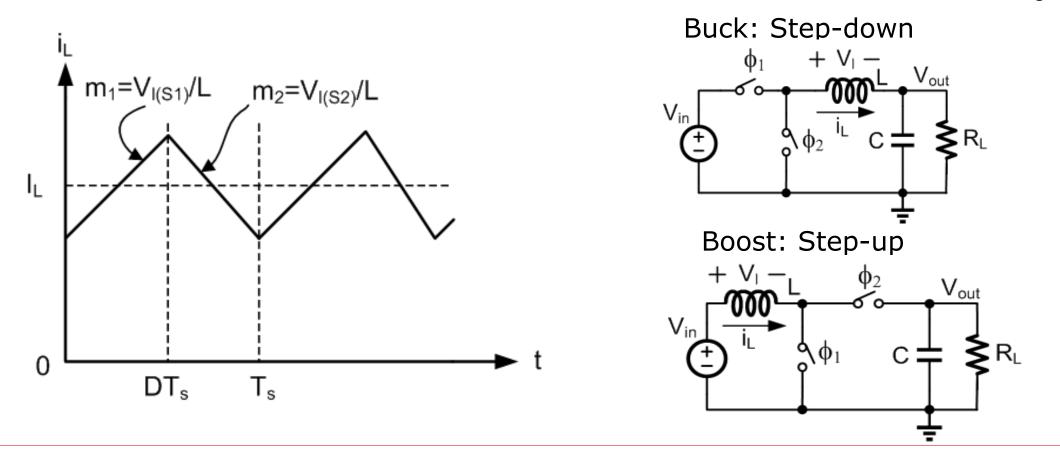

#### Switched-Mode Power Converters

- With different configurations of L and two switches, two most common topologies: buck (step-down) and boost (step-up) in portable applications are illustrated.

- The converter operates in two complementary phases with an inductor for temporary energy storage.

- $\Box$  The converter provides continuous conversion ratio between V<sub>in</sub> and V<sub>out</sub>.

## Characteristics of DC-DC Converters

|                    | Types | Pros                                                                                         | Cons                                                                                                                                 |

|--------------------|-------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Inductor-<br>less  | LDO   | <ul> <li>Simplest and lowest cost</li> <li>Low output noise</li> </ul>                       | <ul> <li>No step-up conversion</li> <li>Poor efficiency if the voltage<br/>mismatch between input and<br/>output is large</li> </ul> |

|                    | SCPC  | <ul> <li>Step up / down conversion</li> <li>Low cost</li> <li>High energy density</li> </ul> | <ul> <li>High switch count</li> <li>Tradeoff between power<br/>efficiency and power density</li> </ul>                               |

| Inductor-<br>based | SMPC  | <ul> <li>Highest power efficiency</li> <li>Step up / down conversion</li> </ul>              | Relatively high cost                                                                                                                 |

#### Outline

□ SMPC Basics and Design Considerations

- Control Methodologies and Design Issues

- Voltage-mode PWM and compensator design

- Current-mode PWM and compensator design

- Current sensor designs

- Gate driver designs

- Hysteretic control

- Advanced Topic

- Three-Level DC-DC Converter

#### **SMPC** Basic

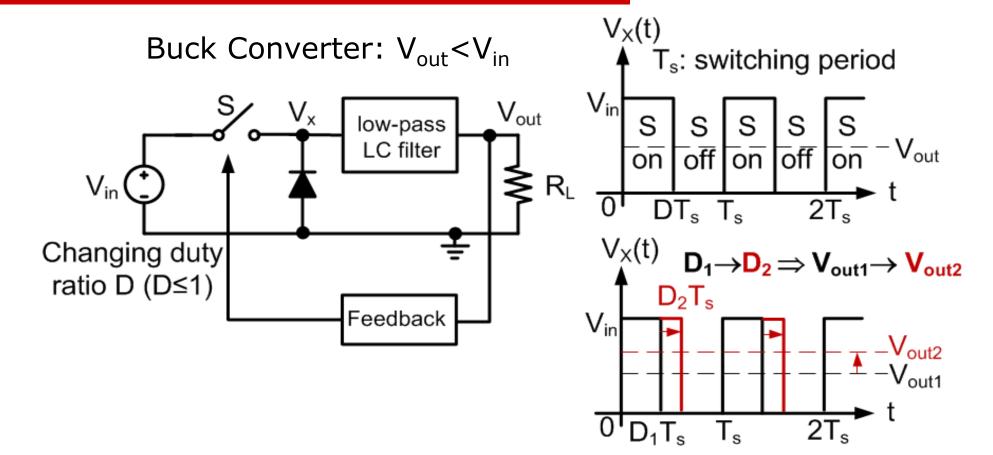

$\Box$  V<sub>out</sub> is a function of duty ratio D ( $0 \le D \le 1$ ) and V<sub>in</sub>.

D Power efficiency  $(\eta) = 100\%$  (ideal) with a lossless switch, diode and LC filter.

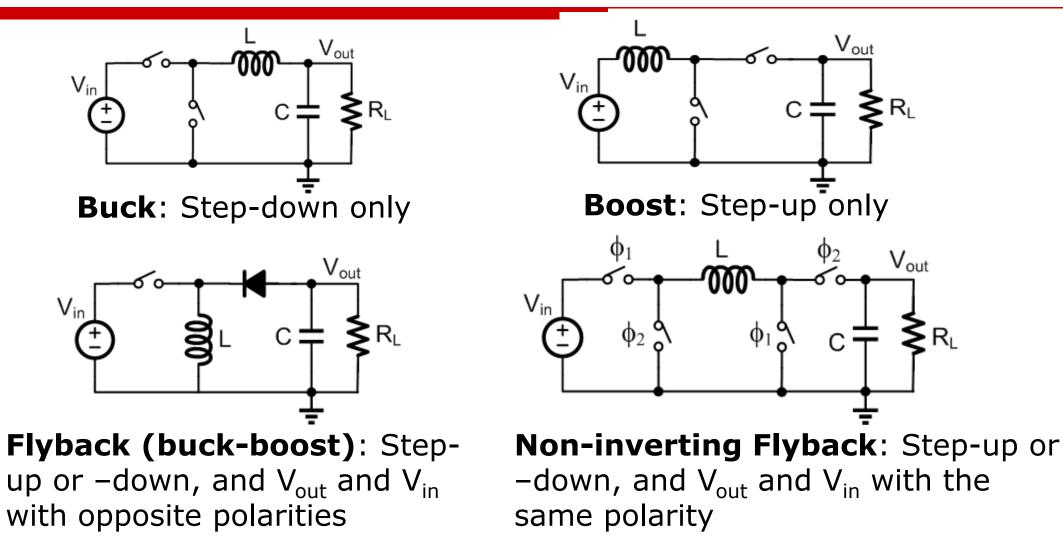

## DC-DC Topologies of SMPC

#### **Continuous Conduction Mode**

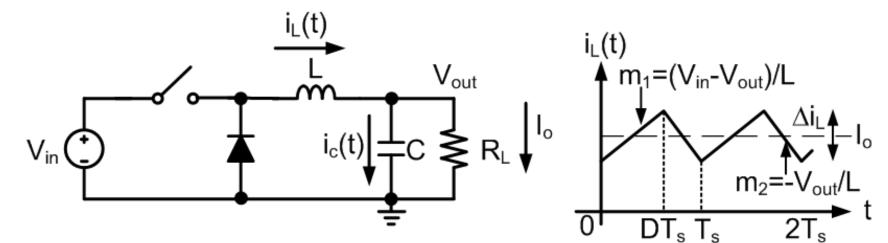

□ The converter operates in continuous conduction mode (CCM) if the inductor current is always larger than 0 in the entire switching period  $T_s$ .

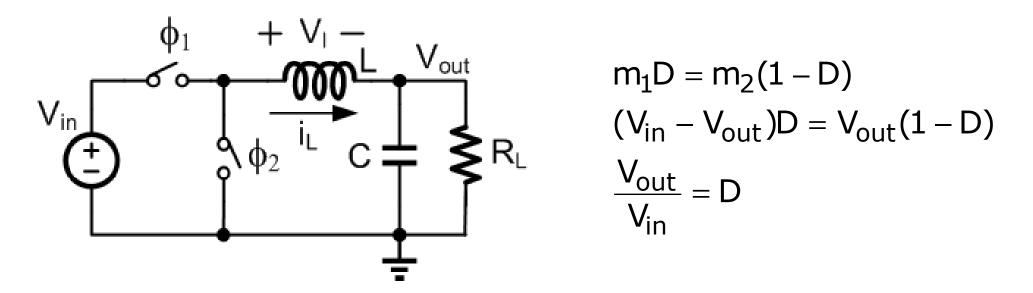

## Buck Converter in CCM

- The voltage conversion ratio can be obtained using Volt-Second Balance.

- □ Note:  $V_1$  in state 1 ( $\phi_1$ ) =  $V_{in} V_{out}$  and  $V_1$  in state 2 ( $\phi_2$ ) =  $-V_{out}$  assuming ideal switches and inductor.

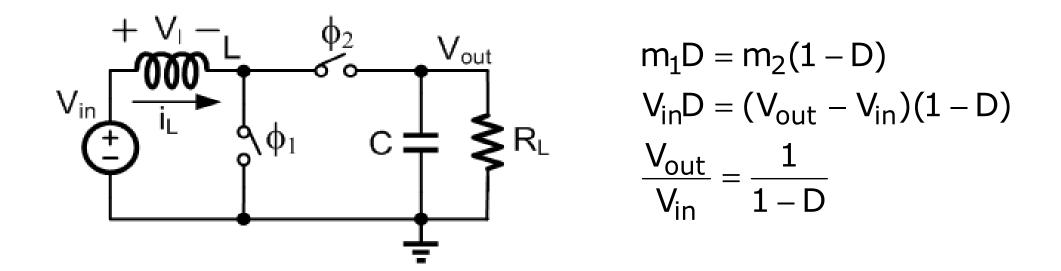

#### Boost Converter in CCM

- The voltage conversion ratio can be obtained using Volt-Second Balance.

- □ Note:  $V_1$  in state 1 ( $\phi_1$ ) =  $V_{in}$  and  $V_1$  in state 2 ( $\phi_2$ ) =  $V_{in}$   $V_{out}$  assuming ideal switches and inductor.

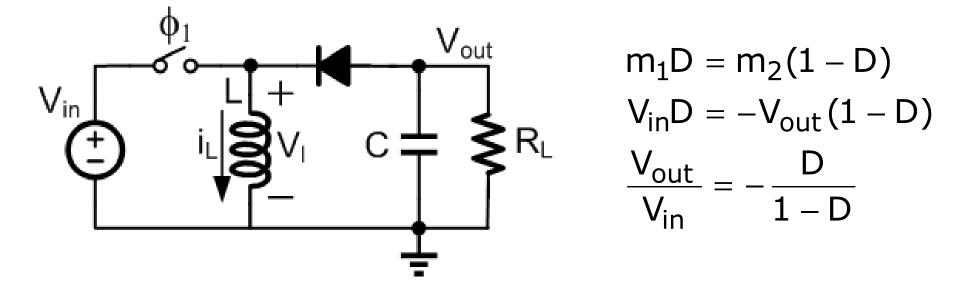

## Flyback Converter in CCM

- The voltage conversion ratio can be obtained using Volt-Second Balance.

- □ Note:  $V_1$  in state 1 ( $\phi_1$ ) =  $V_{in}$  and  $V_1$  in state 2 ( $T_s$   $\phi_1$ ) =  $V_{out}$  assuming ideal switch, diode and inductor.

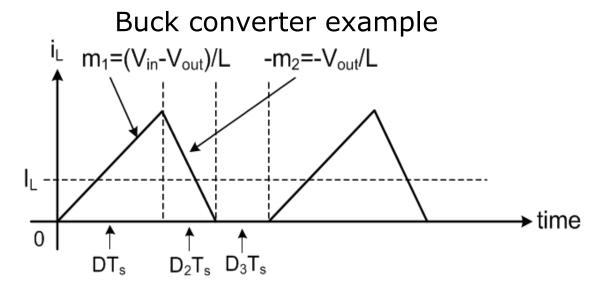

# **Discontinuous Conduction Mode**

When the output current keeps on decreasing, the inductor current would fall to zero and the converter operates in the discontinuous conduction mode (DCM) with a third state S<sub>3</sub>.

**S**<sub>1</sub>:  $nT_s < t < (n+D)T_s$ , switch is on &  $I_L$ increasing **S**<sub>2</sub>:  $(n+D)T_s < t < (n+D+D_2)T_s$ , switch is off &  $I_L$ decreasing **S**<sub>3</sub>:  $(n+D+D_2)T_s < t < (n+1)T_s$ , both active and passive switches are off, and  $I_L = 0$ Note that  $D+D_2+D_3=1$

□ The volt-second balance becomes

$m_1 D = m_2 D_2$

## Performance Requirements of SMPC Design

- □ High Power Conversion Efficiency

- Minimize power losses in the power stage

- □ Small Size (High Power Density) and Low Cost

- Minimize required values of reactive components and off-chip components in the power stage

- High Output Voltage Accuracy

- Improve both line and load regulations

- Minimize output voltage ripple relative to the DC output voltage

- □ Fast Transient Response

- Improve the speed of the controller

- Increase the slew rate of the inductor current

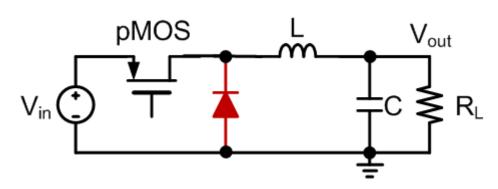

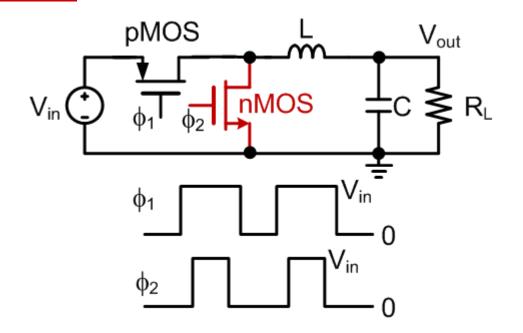

## Asynchronous vs Synchronous Power Stage

- Diode provides a current path when the pMOS switch is off.

- Diode voltage drop leads to large conduction power loss, unsuitable for low output-voltage conditions.

$$\eta_{max} = \frac{V_{out}}{V_{out} + (1 - D)V_d}$$

□ If  $V_{in}$ =3.6V,  $V_{out}$ =1.5V,  $V_d$ =0.7V, then  $\eta_{max}$ =78.6%!

- Power nMOS offers much smaller voltage drop than V<sub>d</sub>.

- Dead-time is needed for gate driving signals of pMOS and nMOS to avoid short-circuit power loss.

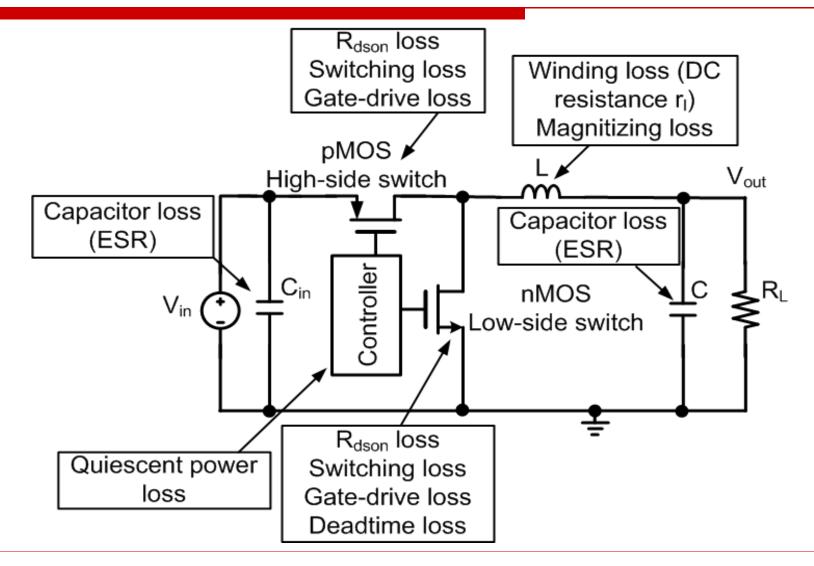

## Losses in Synchronous Buck Converters

## Example on Conduction Loss Calculation

- Conduction loss is dominated by on-resistance of power FETs and DC resistance (DCR) of the inductor.

- Conduction loss of high-side (HS) power switch

$$\begin{split} P_{L-HS} &= I_{HS-rms}^2 \cdot R_{dson-HS} \\ &= I_{L,rms}^2 \cdot D \cdot R_{dson-HS} = (I_0^2 + \frac{\Delta i_L^2}{12}) \cdot D \cdot R_{dson-HS} \end{split}$$

□ Conduction loss of low-side (LS) power switch

$$P_{L-LS} = I_{LS-rms}^{2} \cdot R_{dson-LS}$$

=  $I_{L,rms}^{2} \cdot (1 - D) \cdot R_{dson-LS} = (I_{0}^{2} + \frac{\Delta i_{L}^{2}}{12}) \cdot (1 - D) \cdot R_{dson-LS}$

Conduction loss of inductor DCR  $12^{2}$

## Loss Summary of Synchronous Buck Converter

| Conduction  | Power FET on-<br>resistance R <sub>dson</sub> | $(I_0^2 + \frac{\Delta i_L^2}{12})(R_{dson-HS} \cdot D + R_{dson-LS} \cdot (1 - D))$ |

|-------------|-----------------------------------------------|--------------------------------------------------------------------------------------|

| Losses      | Inductor Winding<br>Resistance                | $(I_0^2 + \frac{\Delta i_L^2}{12})(r_l)$                                             |

| Dynamic     | Power FET Gate Drive<br>Losses                | $f_{s} \cdot V_{in}(C_{g-HS} \cdot V_{g-HS} + C_{g-LS} \cdot V_{g-LS})$              |

| Losses      | Capacitive Switching<br>Loss                  | $\sim 0.5 C_x V_{in}^2 f_s$                                                          |

| Static Loss | Converter quiescent<br>current                | $I_Q \cdot V_{in}$                                                                   |

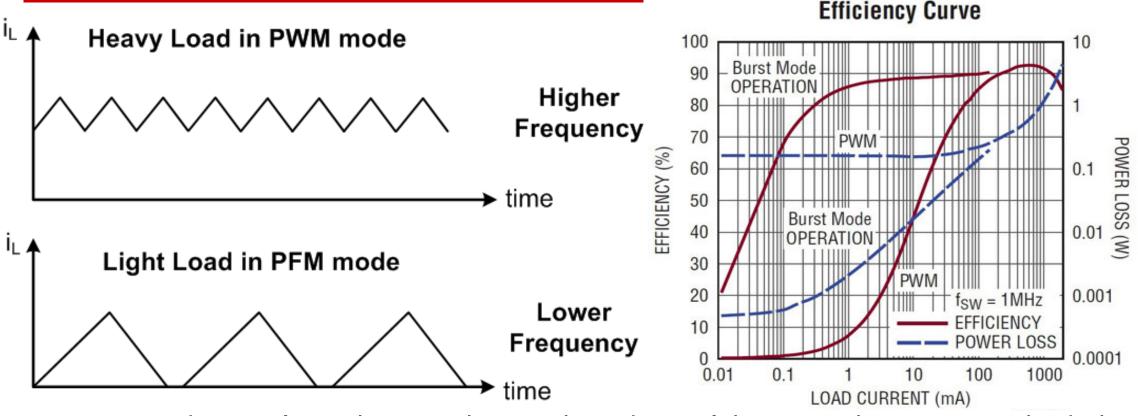

# Efficiency Enhancement: PWM-PFM Control

- Dynamic losses (switching and gate-drive losses) become dominant in the lightload condition.

- Reducing switching activities of power transistors in light loads improves converter light-load power efficiency.

# Efficiency Enhancement: DCM Operation

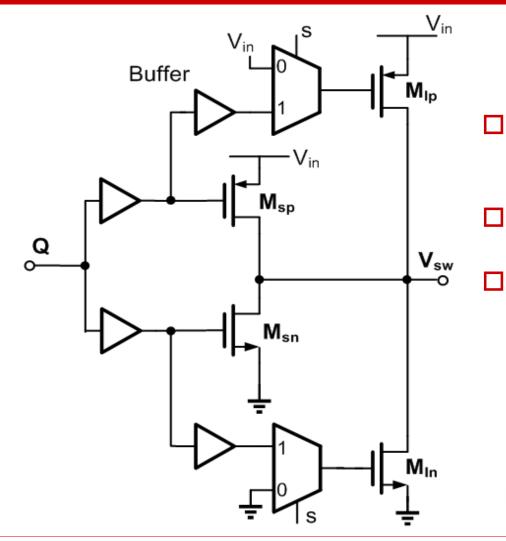

# Efficiency Enhancement: Width Switching

- Only smaller-size power transistors (M<sub>sp</sub>, M<sub>sn</sub>) are used to reduce the gate drive loss at the light load condition.

- All power transistors (M<sub>sp</sub>, M<sub>sn</sub>, M<sub>lp</sub>, M<sub>ln</sub>) are used for the full load condition.

- Potential cross conduction of large and small power transistors may occur during switching if buffers are not designed properly.

D. Park et. al., TCAS-II, Aug. 2014, pp. 599-603.

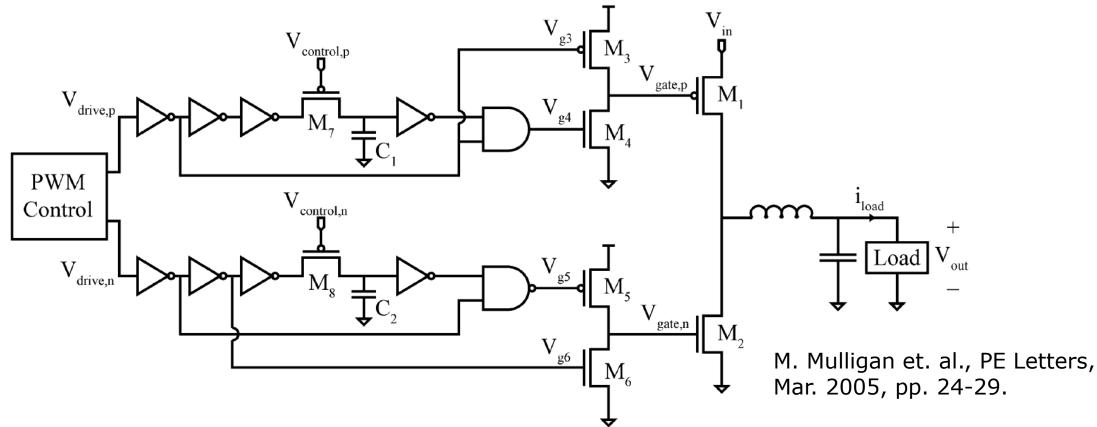

#### Efficiency Enhancement: Gate Swing Modulation

- □ This strategy improves light-load efficiency with the fixed switching frequency.

- Control the gate swing of power transistors via modulating the turn-on time of M<sub>4</sub> and M<sub>5</sub> using a voltage-controlled RC delay

#### Buck Converter: Inductance Selection

For CCM operation,

$$L = \frac{(V_{in} - V_{out}) \cdot D}{\Delta i_L f_s} = \frac{(V_{in} - V_{out}) \cdot V_{out}}{V_{in} \cdot \Delta i_L \cdot f_s} = \frac{(V_{in} - V_{out}) \cdot V_{out}}{V_{in} \cdot r \cdot I_{o,max} \cdot f_s}$$

where r is the current ripple ratio of 0.25 - 0.5 I<sub>o.max</sub>: maximum output current

For given  $V_{in}$  and  $V_{out}$ , the inductance is determined by the inductor current ripple and switching frequency  $f_s$ . Higher switching frequency  $f_s$  reduces the required L.

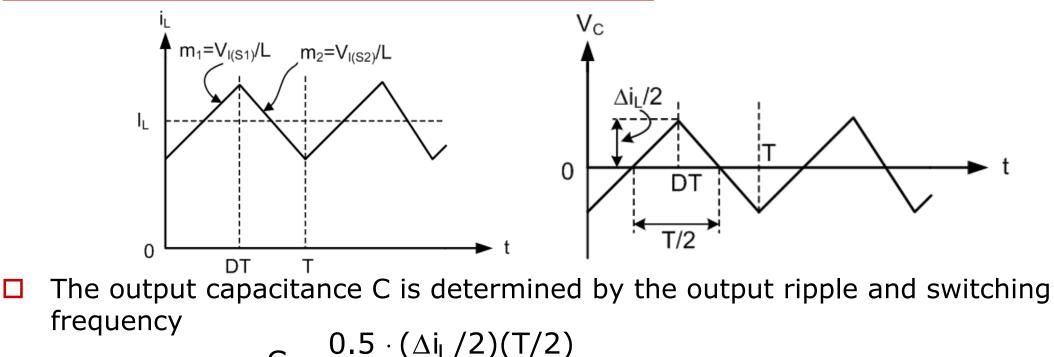

#### Buck Converter: Output Capacitor Selection

$$\begin{split} \mathsf{C} &= \frac{0.5 \cdot (\Delta i_{L}/2)(T/2)}{\Delta V_{out}} \\ &= \frac{(\mathsf{V}_{in} - \mathsf{V}_{out}) \cdot \mathsf{D}}{8L\Delta V_{out} f_{s}^{2}}, \quad \Delta V_{out} \text{ : output ripple voltage} \end{split}$$

$\Box$  Higher switching frequency reduces the required value of C for a given  $\Delta V_{out}$ .

## Outline

□ SMPC Basics and Design Considerations

- Control Methodologies and Design Issues

- Voltage-mode PWM and compensator design

- Current-mode PWM and compensator design

- Current sensor designs

- Gate driver designs

- Hysteretic control

- □ Advanced Topic

- Three-Level DC-DC Converter

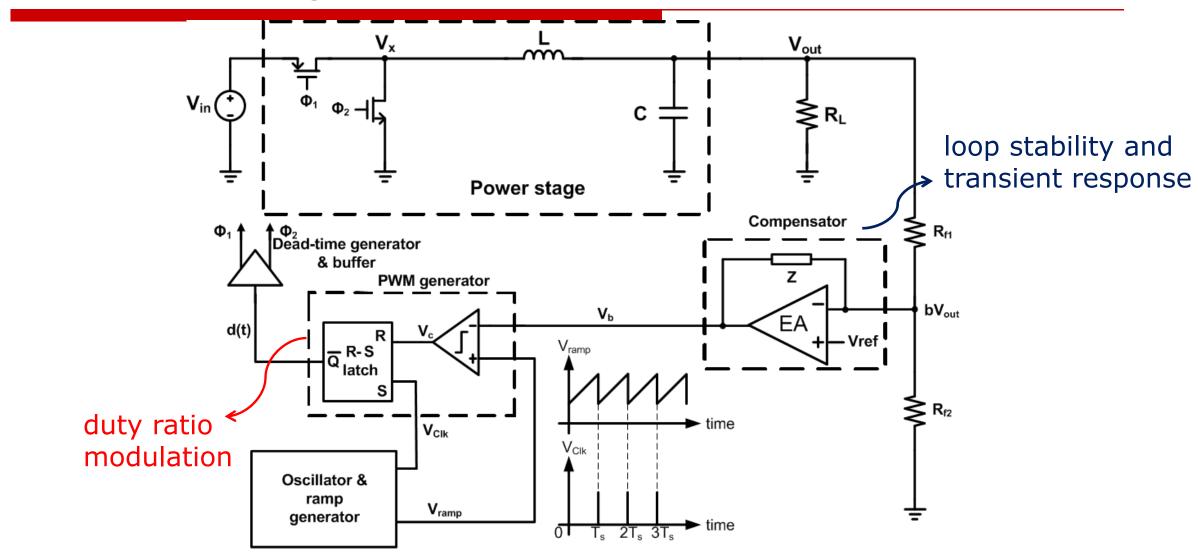

#### PWM – Voltage-Mode Control (VMC)

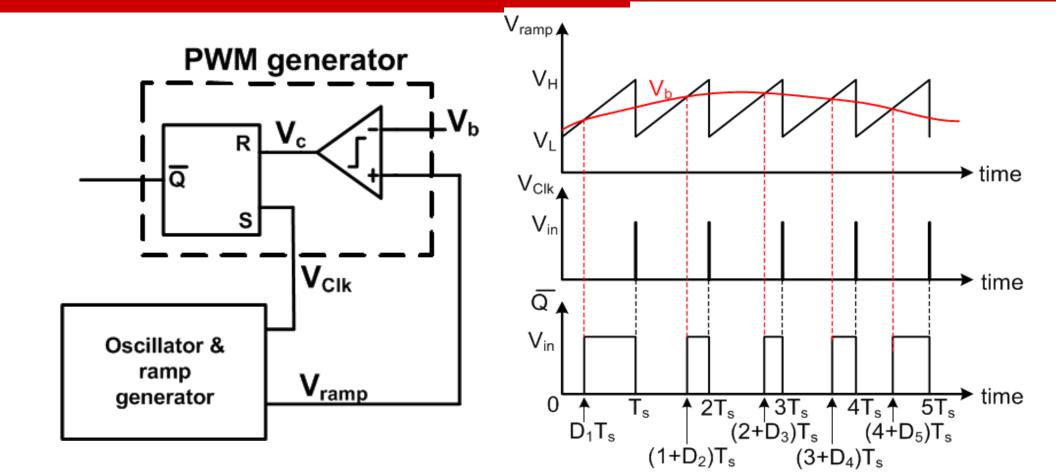

#### VMC – PWM Generator

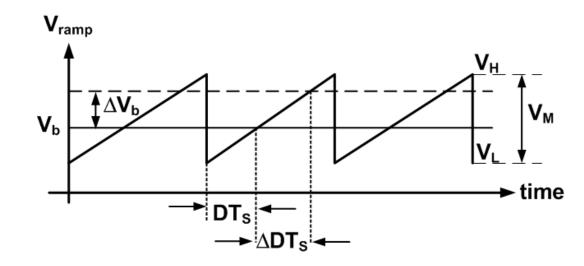

Duty ratio (D) is defined by the crossing of compensator output  $V_b$  and the fixed ramp signal  $V_{ramp}$ : larger  $V_b$  leads to larger D.

# VMC – Loop Gain T(s) (1)

#### Loop gain T(s)

A(s): Compensator transfer function C(s): Control-to-output transfer function

#### PWM generator transfer function ( $\Delta D/\Delta V_b$ )

## VMC – Traditional Dominant Pole Compensation

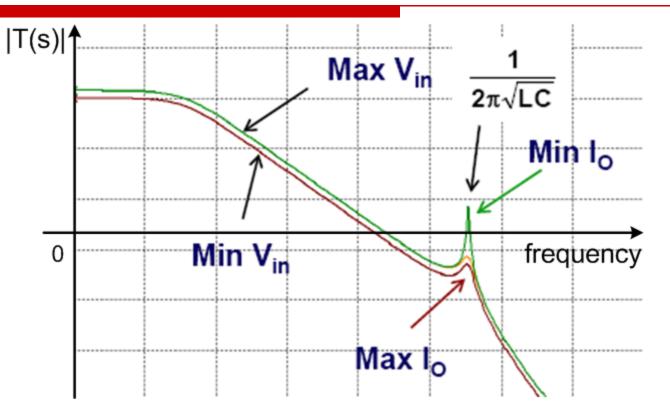

- High Q factor of the complex poles limits the unity-gain frequency of T(s), thereby degrading the converter transient response.

- □ Worst-case stability (minimum gain margin) occurs at the maximum  $V_{in}$  and the minimum  $I_o$  due to largest Q value of the complex poles.

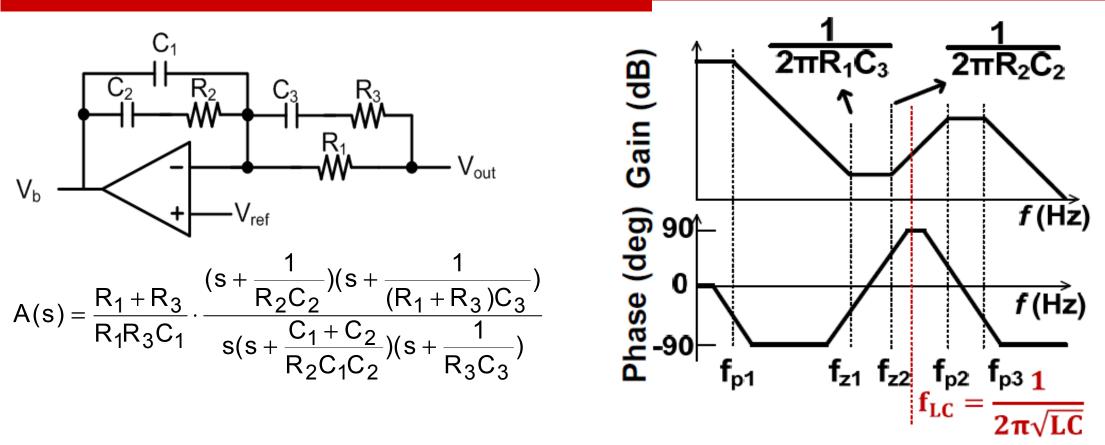

## VMC – Type III Compensator (1)

- 2 LHP zeros are generated in A(s) to compensate for the negative phase shift of the complex poles in C(s).

- This compensator however requires large area for passive components.

## VMC – Type III Compensator (2)

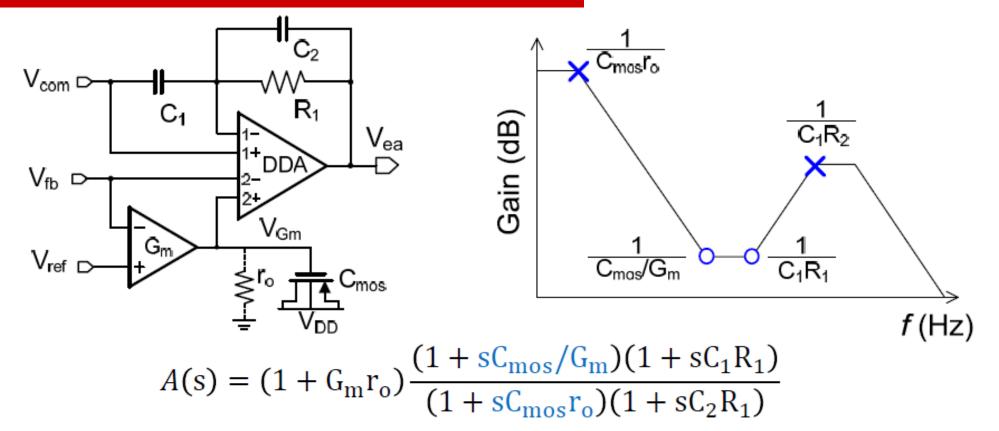

Differential difference amplifier is used to realize the Type-III compensator for reducing the required number of passive components.

L. Chen et. al., ISSCC, Feb. 2014, pp. 84-85.

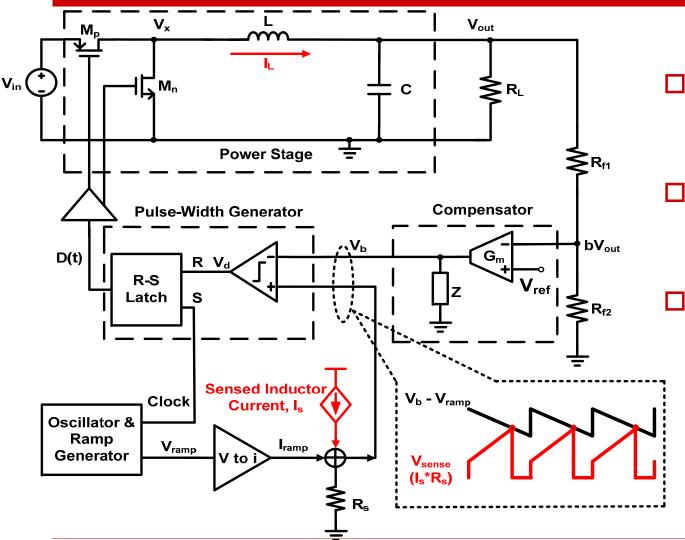

#### PWM – Current-Mode Control (CMC)

- Both inductor current and output voltage information are used.

- The converter has inherent pulse-bypulse current limiting and soft start.

- Sensed inductor current is used as a ramp to define D by replacing the fixed voltage ramp.

```

C. F. Lee et. al., JSSC, Jan. 2004, pp. 3-14.

```

## CMC – Sub-Harmonic Oscillations (1)

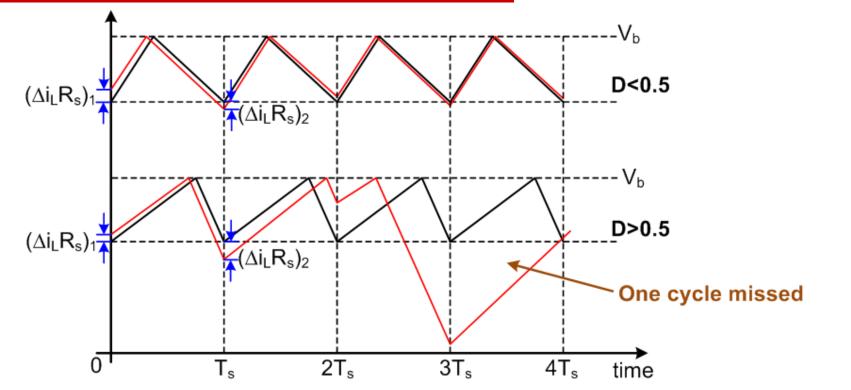

□ Current-mode converters will undergo sub-harmonic oscillation (at  $f_s/2$ ,  $f_s/4$ , etc.) whenever D > 0.5.

□ For D < 0.5,  $m_1 > m_2$ , the perturbation decreases with  $(\Delta i_L R_f)_2 < (\Delta i_L R_f)_1$ .

□ For D > 0.5,  $m_1 < m_2$ , the perturbation increases with  $(\Delta i_L R_f)_2 > (\Delta i_L R_f)_1$ .

## CMC – Sub-Harmonic Oscillations (2)

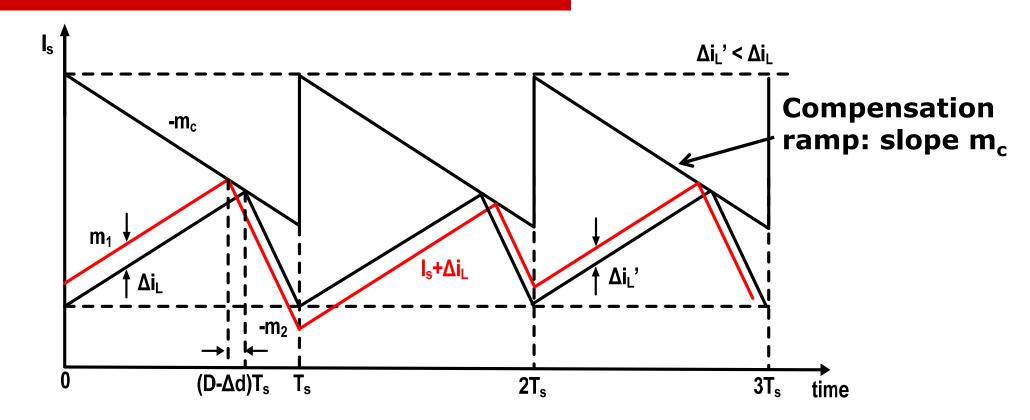

A compensation ramp with slope  $m_c \ge m_{2,max}/2 = V_{out,max}/2L$ , can suppress the oscillation under D>0.5, where  $m_2$  is the slope of the  $I_L$  during (1-D) $T_s$ .

□ The compensation ramp can be realized by the voltage ramp generator.

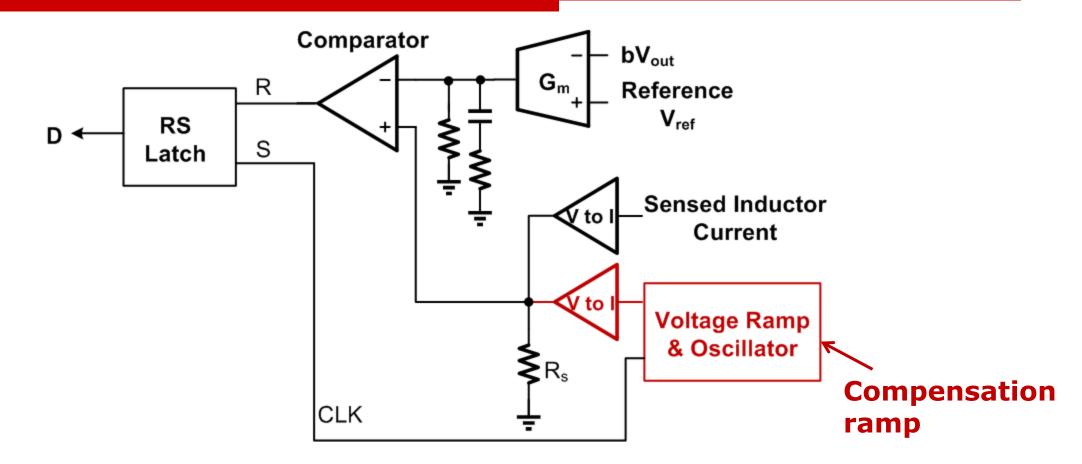

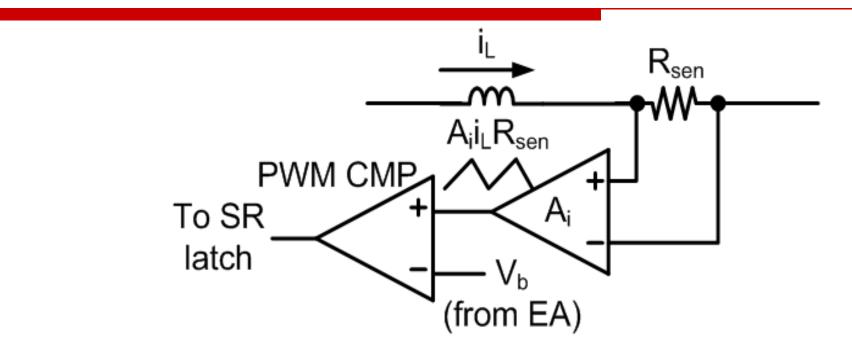

## Compensation Ramp in Current-Mode Controller

The compensation ramp with slope m<sub>c</sub> is added together with the sensed inductor current signal at the input of PWM generator.

$$\begin{split} \mathsf{T}(s) &= \frac{\mathsf{R}_{f2}}{\mathsf{R}_{f1} + \mathsf{R}_{f2}} \mathsf{A}(s) \frac{\mathsf{R}_L // \mathsf{R}_a}{\mathsf{R}_s} \frac{1 + s\mathsf{R}_{eC}\mathsf{C}}{(1 + s \, / \, \omega_a)(1 + s \, / \, \omega_{t1})} & \mathsf{R}_{eC}: \mathsf{ESR} \text{ of output capacitor} \\ \mathsf{R}_a &= \frac{\mathsf{L}}{\mathsf{I}(1 - \mathsf{D})(1 + \frac{\mathsf{m}_c}{\mathsf{m}_1}) - \mathsf{D}]\mathsf{T}_s} & \mathsf{A}(s): \mathsf{transfer function of the compensator} \\ \omega_a &= \frac{1}{\mathsf{C}(\mathsf{R} \, // \, \mathsf{R}_a)} = \mathsf{p}_1 \\ \omega_{t1} &= \frac{1}{(1 - \mathsf{D})(1 + \frac{\mathsf{m}_c}{\mathsf{m}_1})\mathsf{T}_s} = \mathsf{p}_2 \end{split}$$

Two separate poles  $\omega_a$  and  $\omega_{t1}$  in T(s) are easier to compensate compared to the complex poles in the voltage-mode counterpart.

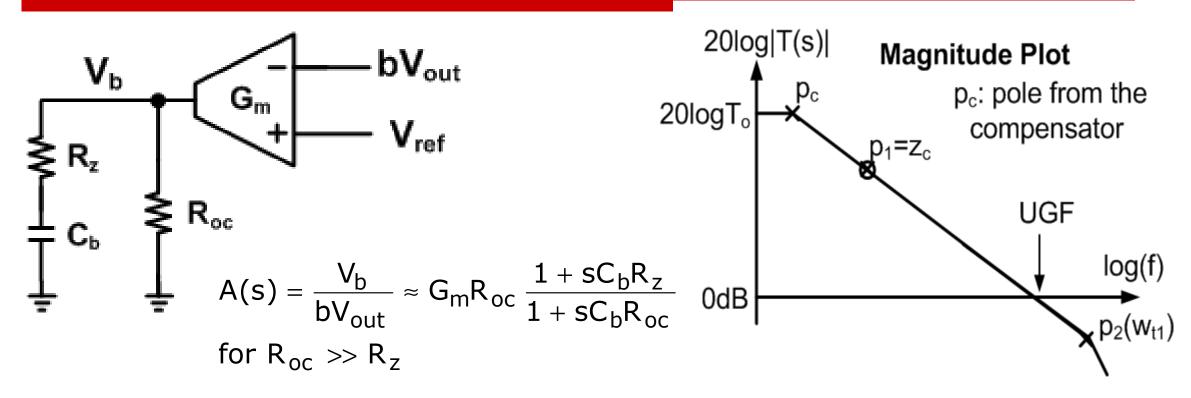

## CMC – Compensator Design

- Compensator LHP zero ( $z_c$ ) cancels negative phase shift of  $p_1(\omega_a)$  in T(s) by positioning  $z_c$  at  $p_1$ .

- Dominant pole  $p_c$  of T(s) is given as  $1/R_{oc}C_b$  from the compensator.

- $\Box$  UGF of T(s) is smaller than  $\omega_{t1}$  and can reach 4 or 5 times less than  $f_s$ .

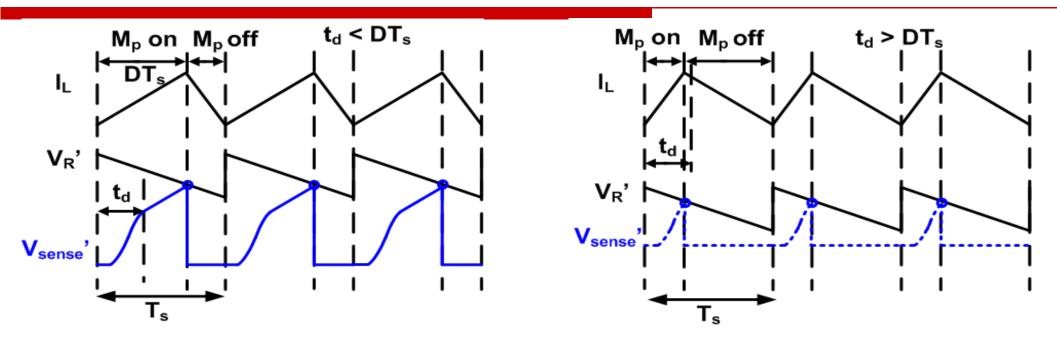

## Inductor Current Sensing

□ Speed of inductor current sensing can limit the maximum switching frequency  $(f_{s,max})$  and duty ratio range of the converter.

- CMC converter can function properly if the delay  $(t_d)$  of the current sensor is smaller than  $D_{min} * 1/f_{s,max}$ .

- Power dissipation of the current sensor should be minimized.

## Sensing Resistor

$\Box$  Sensing resistor R<sub>sen</sub> in series with the inductor to provide entire inductor profile.

- □ If R<sub>sen</sub> is too small, inductor current cannot be detected in light-load condition.

- If  $R_{sen}$  is too large (e.g. 500m $\Omega$ ), conduction loss of  $R_{sen}$  might significantly increase the total power loss.

- If  $i_{L,rms} = 1A$ , the loss due to  $R_{sen} = 500$  mW that is not suitable for low-power applications.

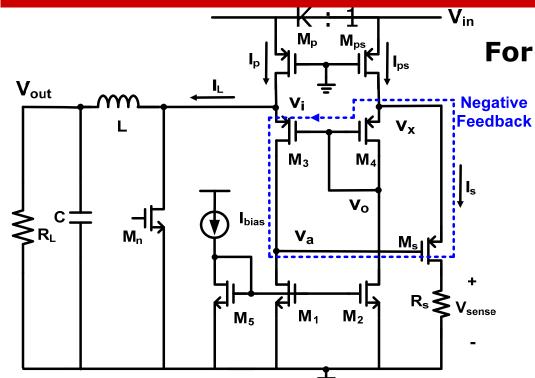

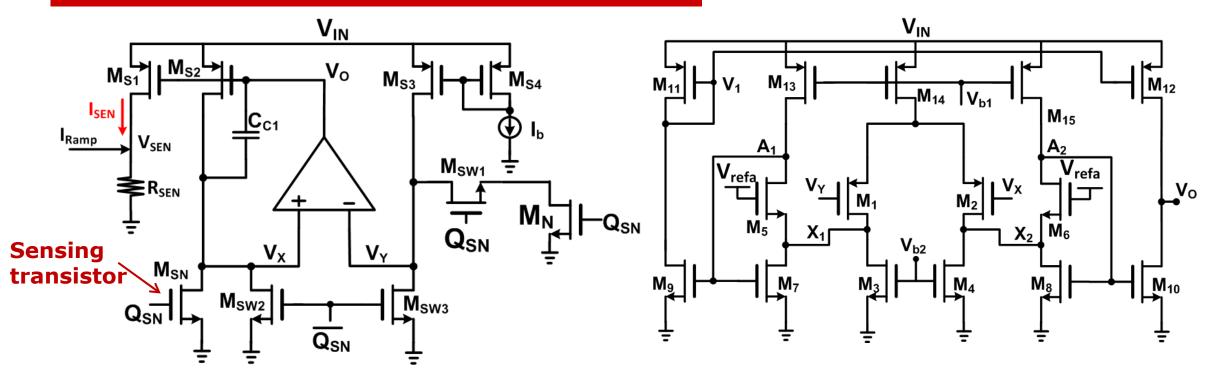

## Switch Current Sensing for HS Power pMOS

For peak current control in Buck converters

Operation in state DT<sub>s</sub>

$$V_{sense} = I_s \cdot R_s \approx \frac{I_p}{K} \cdot R_s = \frac{I_L}{K} \cdot R_s$$

K>>1 and is commonly selected as 1000

Sensing transistor M<sub>ps</sub> tracks current through high-side power FET M<sub>p</sub> during state 1.

Since I<sub>S</sub> << I<sub>L</sub>, the switch current sensing is "lossless" compared to the load current.

The speed of the current sensing is typically limited by the non-dominant pole of the negative feedback loop.

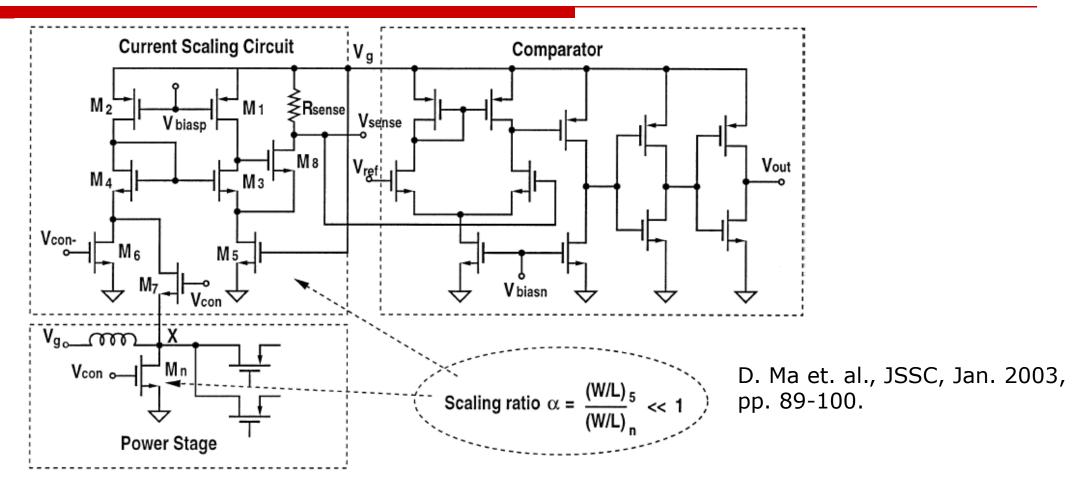

## Switch Current Sensing for LS Power nMOS

Low-side sensing: sensing transistor M<sub>5</sub> tracks current through low-side power nFET M<sub>n</sub> during state 1 for the peak current control in Boost converters.

## Low-Voltage Switch Current Sensing

Low-voltage current sensor for Boost converters

LV error amplifier

Low-voltage low-side current sensor relies on using a low-voltage error amplifier for obtaining scaled-down sensed current through power nFET M<sub>N</sub>.

D. Park et. al., TCAS-II, Aug. 2014, pp. 599-603.

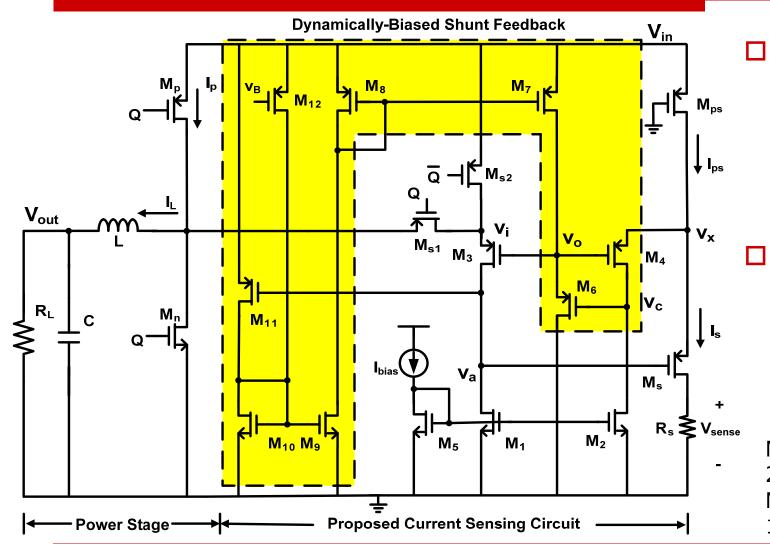

# High-Speed Switch Current Sensing

- **Dynamically-biased shunt feedback** uses 7 additional transistors to push the nondominant pole in the feedback loop to a higher frequency.

- The UGF of the feedback loop is increased, thereby minimizing the sensing delay for higher f<sub>s</sub>.

M. Du et. al., TCAS-I, Oct. 2010, pp. 2804-2814.M. Du et. al., JSSC, Aug. 2011, pp. 1928-1939.

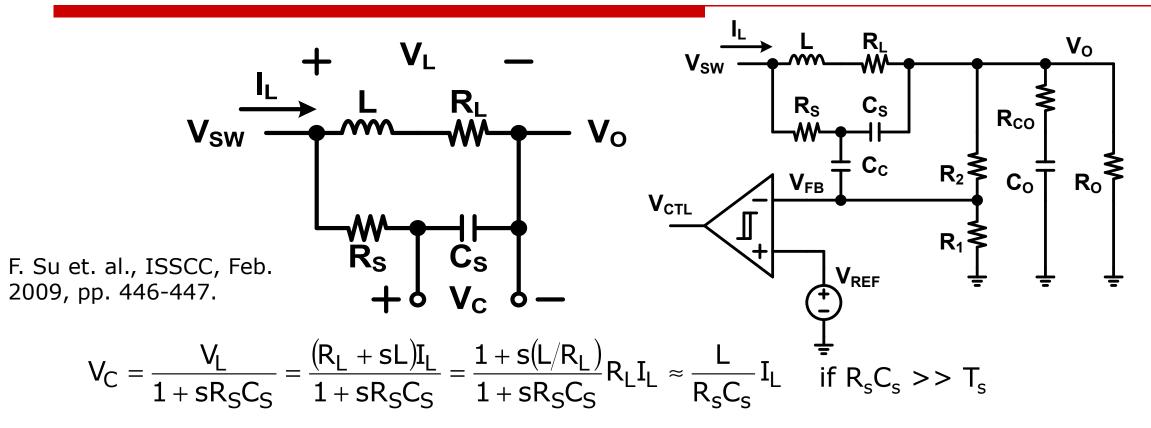

## Filter-Based Current Sensing

- Capacitor voltage V<sub>C</sub> of a lossless low-pass filter formed by R<sub>S</sub> and C<sub>S</sub> in parallel with the inductor provides inductor current information.

- This current sensor provides high-speed current sensing and is suitable for high-frequency (of over 10MHz) DC-DC converters.

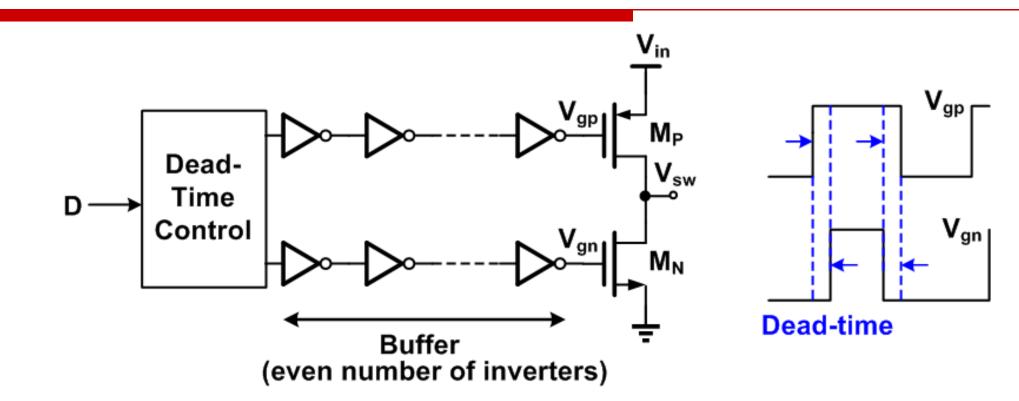

## Gate Driver for HS Power pMOS

- □ Gate driver structure: dead-time control and digital buffers (for LV synchronous converters with a high-side power pMOS and a low-side nMOS).

- Dead-time avoids simultaneous conduction of power transistors during switching transitions, removing the short-circuit loss.

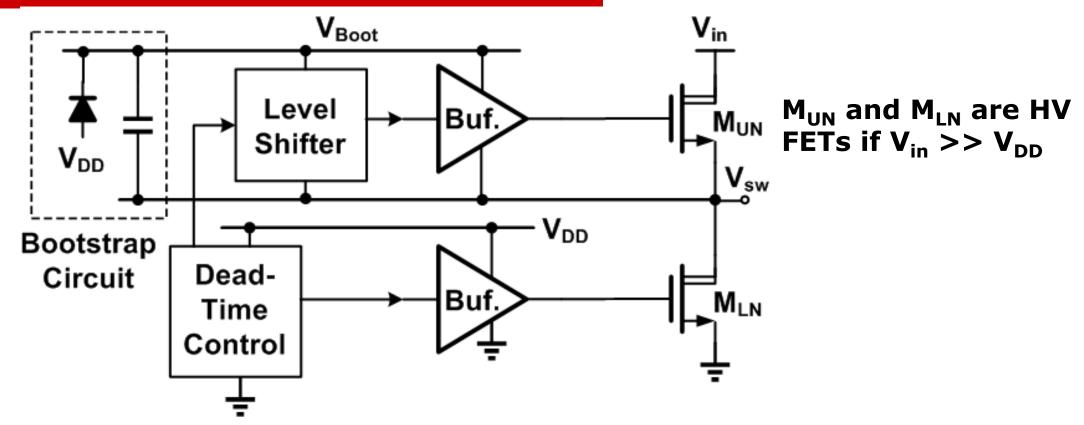

# Gate Driver for High-Side Power nMOS (1)

With a high-side power nMOS, the gate driver needs to have an additional level shifter and bootstrap circuit.

□ Bootstrap supply  $V_{BOOT}$  (=  $V_{IN}$  +  $V_{DD}$ ) is realized by a diode and a capacitor.

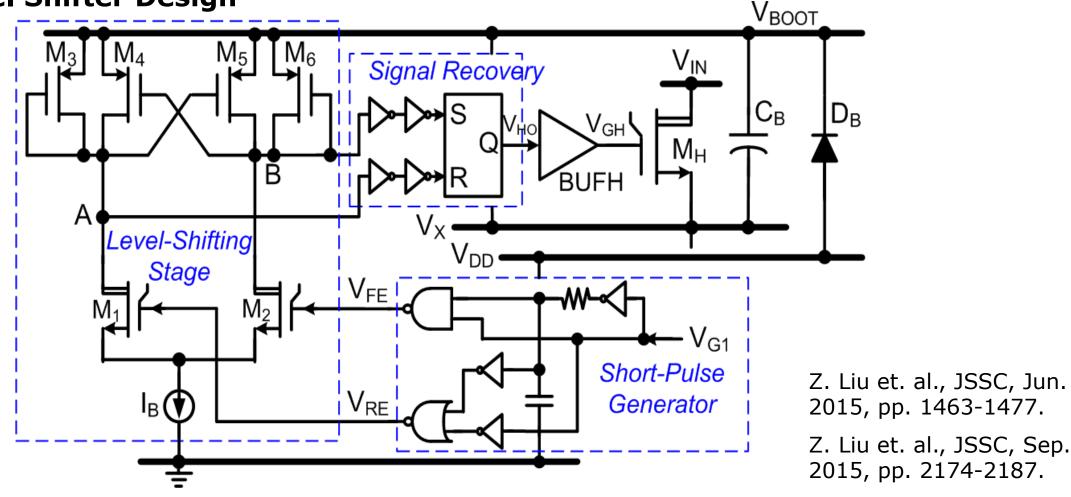

# Gate Driver for High-Side Power nMOS (2)

#### **Level Shifter Design**

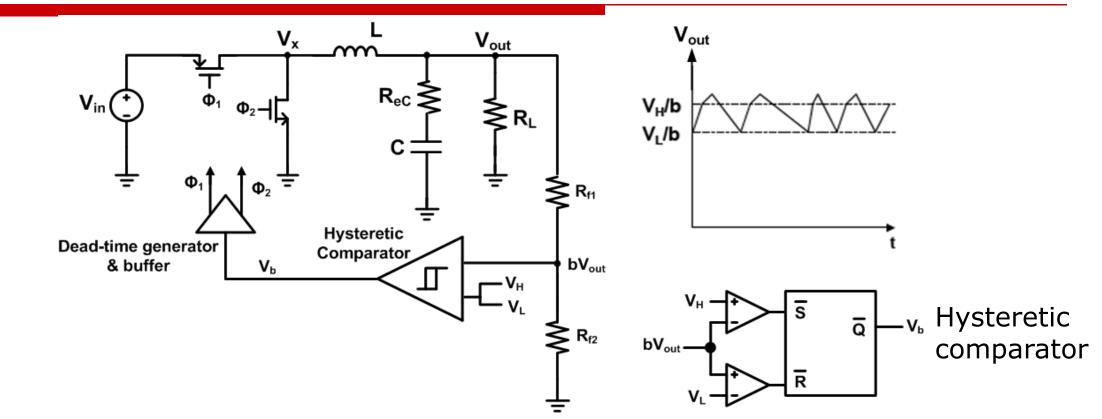

## Hysteretic Control

- Compared to PWM control, hysteretic control improves the converter load transient response without using the bandwidth-limited error amplifier in the controller.

- Cons: large output ripple and unpredictable output noise spectrum with variable switching frequency

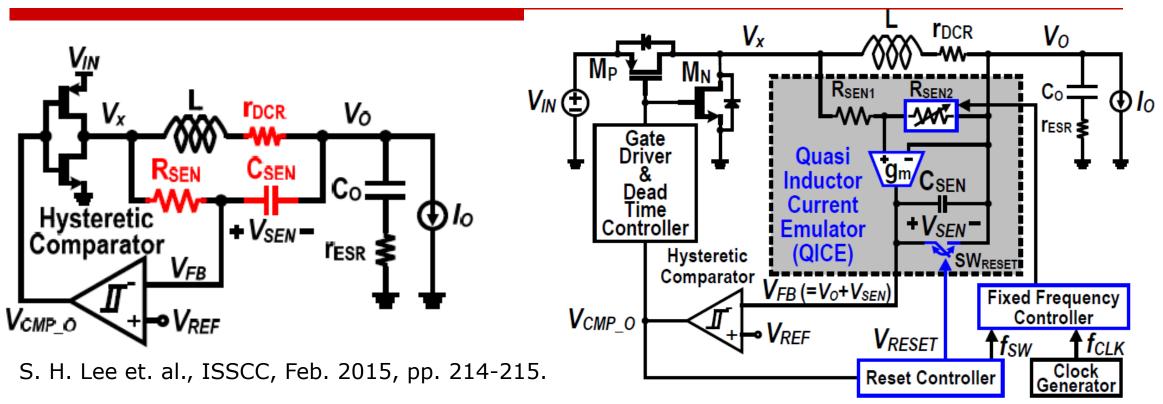

#### Current-Mode Hysteretic Control

- Current-mode hysteretic control (CMHC) offers smaller output ripple but slower transient response compared to voltage-mode counterpart.

- Quasi-current-mode hysteretic control improves transient response and reduces the required current sensing capacitance C<sub>SEN</sub> compared to CMHC.

## Outline

□ SMPC Basics and Design Considerations

- □ Control Methodologies and Design Issues

- Voltage-mode PWM and compensator design

- Current-mode PWM and compensator design

- Current sensor designs

- Gate driver designs

- Hysteretic control

- Advanced Topic

- Three-Level DC-DC Converter

#### Three-Level DC-DC Converter (1)

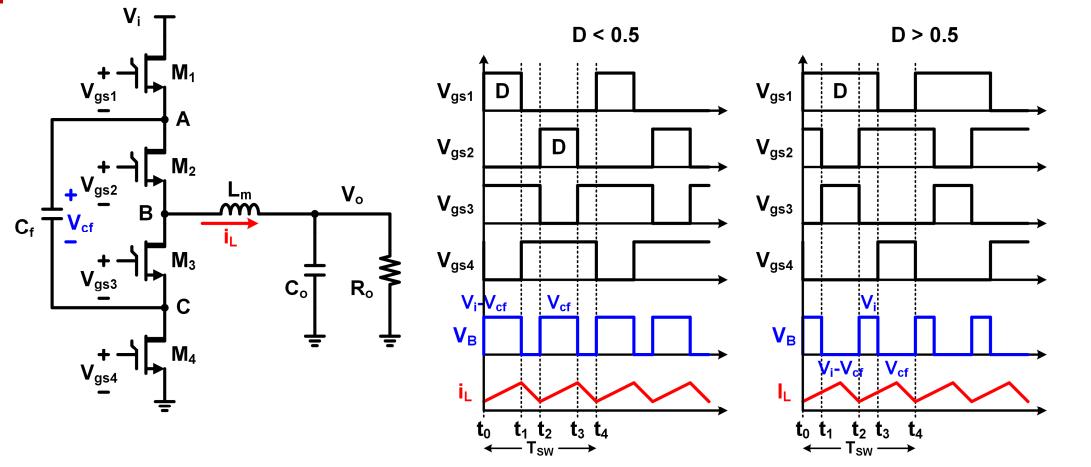

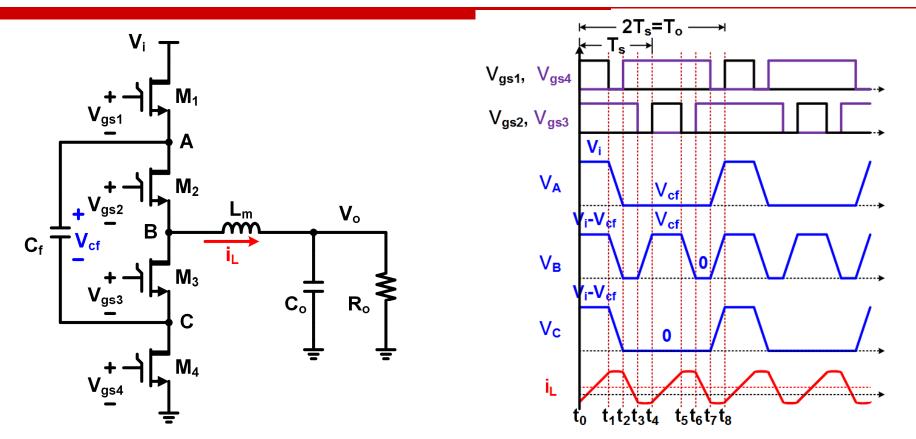

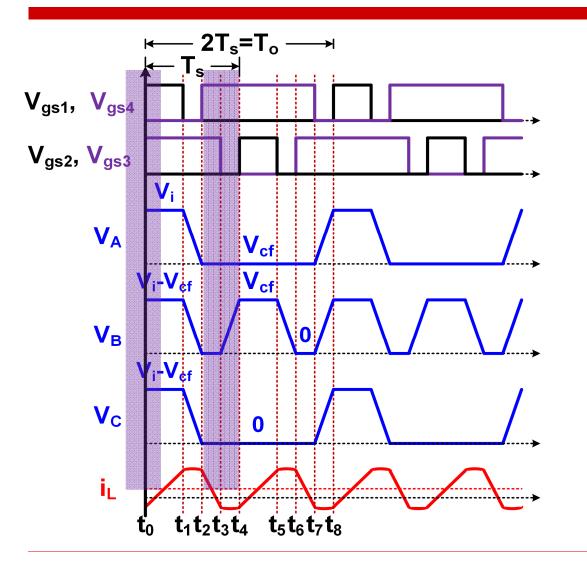

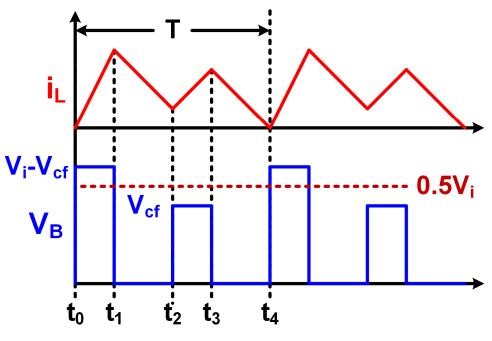

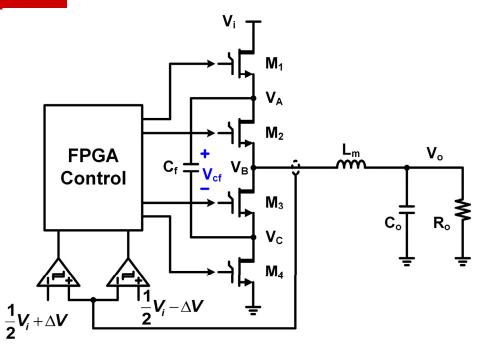

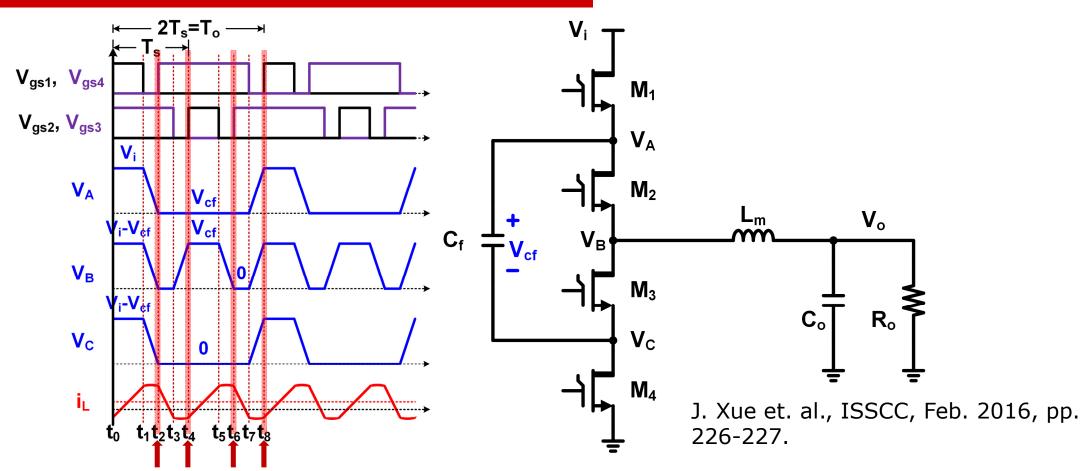

A three-level converter has four power FETs ( $M_1 - M_4$ ) and a flying capacitor  $C_f$  connected between nodes A and C with its voltage  $V_{cf} = 0.5V_i$  in the steady state.

#### Three-Level DC-DC Converter (2)

The frequency of both inductor current and output voltage is 2 times larger than gate drive signals.

The voltage swing at each switching node is only  $V_i/2$  if  $V_{cf} = V_i/2$ .

#### Three-Level DC-DC Converter (3)

**Duty Ratio**

Duty Ratio

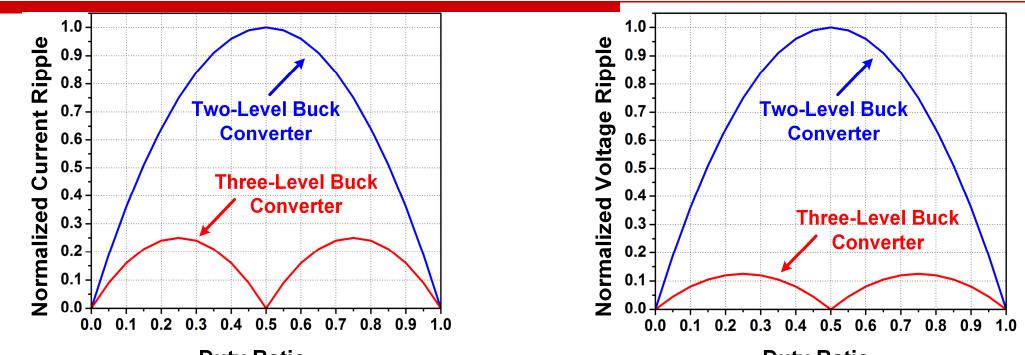

Compared to a two-level converter, the three-level converter

- reduces the required inductor value by 4 times

- reduces the required output capacitor value by 2 times

- reduces the voltage stress across each power switch by 2 times ⇒ smaller-size lower voltage rating power FETs can be used ⇒ suitable for HV applications

#### Voltage across the Flying Capacitor

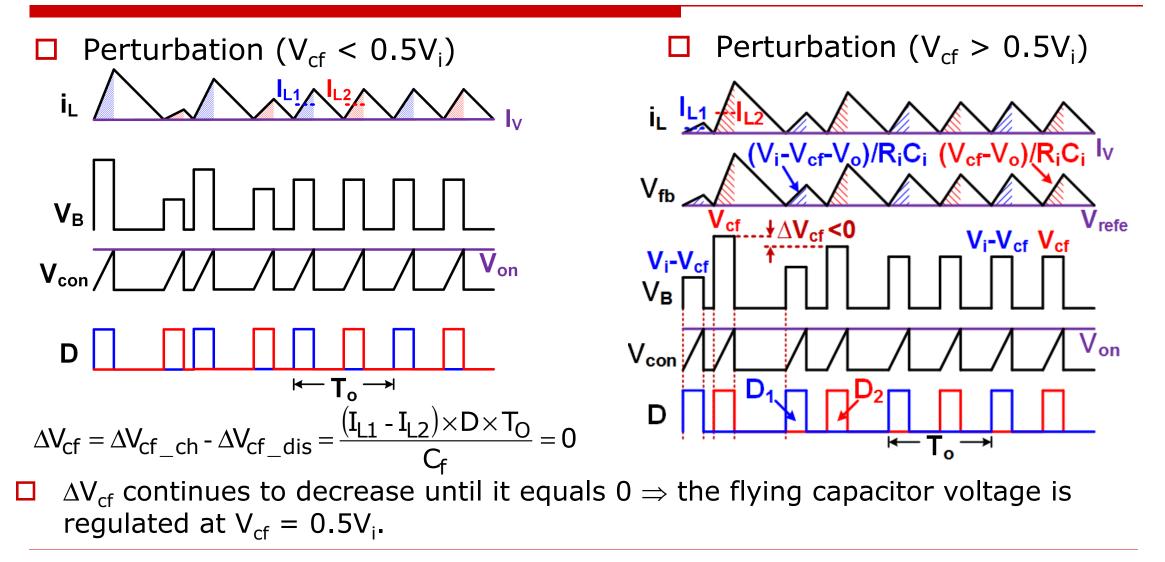

$\Box \Delta V_{cf}$  in charging phase

$$\Delta V_{cf\_ch} = \frac{I_{L1} \times D_1 \times T_0}{C_f}$$

$\Box \Delta V_{cf}$  in discharging phase

$$\Delta V_{cf\_dis} = \frac{I_{L2} \times D_2 \times T_0}{C_f}$$

$\Box \Delta V_{cf}$  in one period  $T_o$

$$\Delta V_{cf} = \Delta V_{cf\_ch} - \Delta V_{cf\_dis} = \frac{(I_{L1} - I_{L2}) \times D \times T_{O}}{C_{f}}$$

### Flying Capacitor Balancing

Flying capacitor unbalanced

Control of flying capacitor balancing

- □ The unbalanced behavior of the flying capacitor would damage the power FETs.

- □ Comparator-based balancing scheme with two external reference voltages can force  $V_{cf}$  close to  $V_i/2$ , and it is suitable for low-voltage applications.

### Flying Capacitor Self Balancing (1)

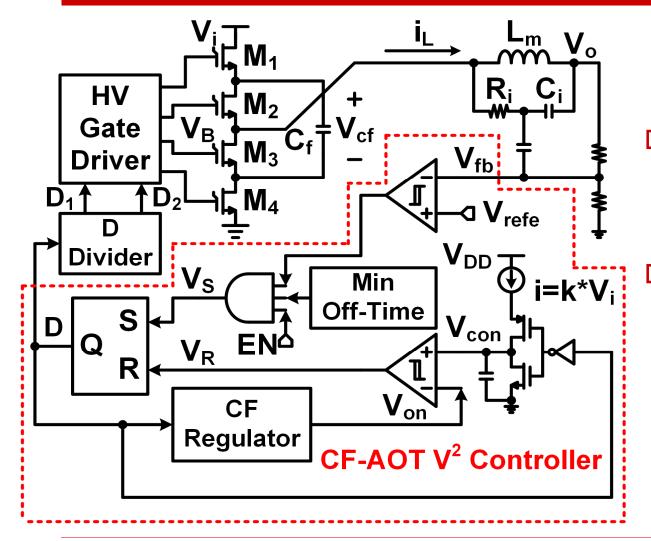

- Self-balancing means that both flying capacitor balancing and output voltage regulation are achieved simultaneously by the same controller.

- By regulating the average inductor current, both V<sub>cf</sub> and V<sub>o</sub> would be regulated automatically.

J. Xue et. al., ISSCC, Feb. 2016, pp. 226-227. J. Xue et. al., JSSC, Dec. 2016, pp. 2854-2866.

### Flying Capacitor Self Balancing (2)

## Loop Gain of Three-Level Converters

□ The loop gain T(s) of the three-level converter

$$T(s) = b \cdot A(s) \cdot \frac{V_{in}}{V_M} \cdot \frac{1}{1 + s \frac{L}{R} + s^2 LC}$$

Note: b is the feedback resistor ratio

A(s) is the transfer function of the compensator

$V_M$  is the amplitude of the ramp signal

- The loop gain of the three-level converter is the same as that of twolevel converter.

- Same controller type as the two-level converter can be used for the three-level converter.

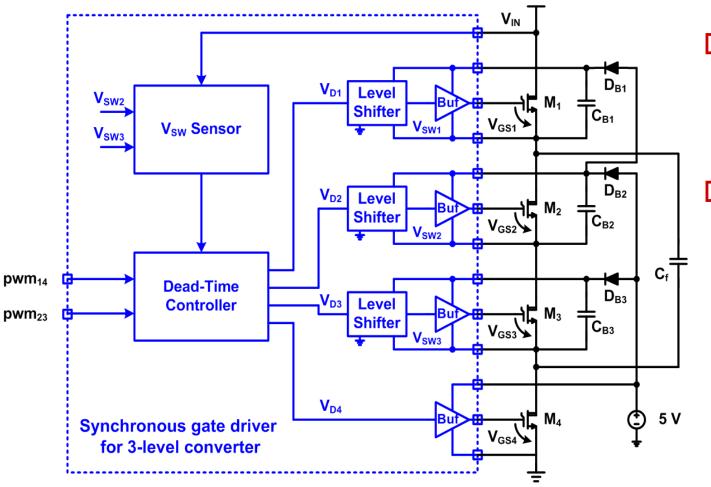

## Gate Driver for Three-Level Converters

Driver structure: 3 level shifters, 4 voltage buffers, 3 sets of bootstrap circuitry, and a dead-time controller

In LV applications, open-loop fixed dead-time is used to remove the shoot-through current of power FETs and V<sub>SW</sub> sensor is not necessary.

L. Cong et. al., ECCE, Sep. 2015, pp. 1479-1484.

J. Xue et. al., APEC, Mar. 2015, pp. 451-454.

#### Example: 100V Three-Level DC-DC Converter (1)

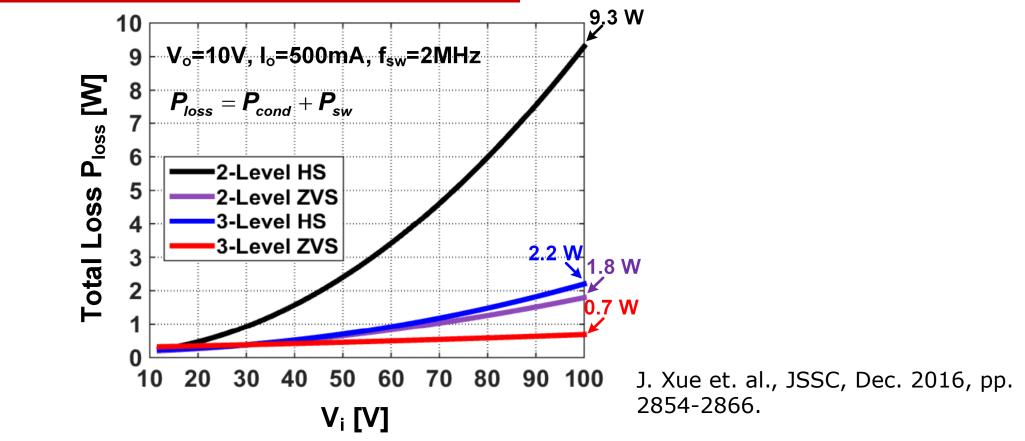

□ In high-input applications, all power FETs can realize ZVS during turn-on with negative inductor current using a small-size inductor.

### Example: 100V Three-Level DC-DC Converter (2)

□ The three-level ZVS converter has the lowest power loss under high inputs

- 13 times reduction compared to the two-level hard switching converter at  $V_i = 100V$

- 2.6 times reduction compared to the two-level ZVS converter at  $V_i = 100V$

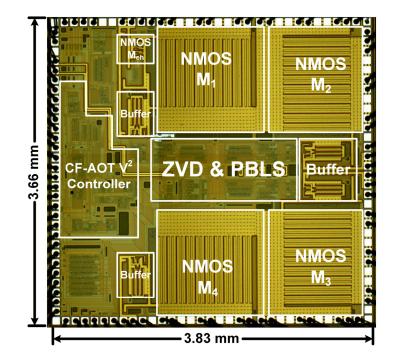

## Example: 100V Three-Level DC-DC Converter (3)

0.5-µm 120-V AMS CMOS process

|                                      | TI LM5007                                                                | This Work                                                                                                |

|--------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Process                              | N. A.                                                                    | 0.5-µm 120-V CMOS                                                                                        |

| Topology                             | Two-Level, Asyn.                                                         | Three-Level, Syn.                                                                                        |

| Power FETs Stress                    | V <sub>i</sub>                                                           | $0.5V_i (V_i = 26 V - 100 V)$                                                                            |

| Input Voltage (V)                    | 12 – 75                                                                  | 12 - 100                                                                                                 |

| Output Voltage (V)                   | 10                                                                       | 10                                                                                                       |

| Output Power (W)                     | 4                                                                        | 5                                                                                                        |

| Duty Ratio                           | 0.13 - 0.83                                                              | 0.11 - 0.83                                                                                              |

| Capacitor Balancing                  | N. A.                                                                    | Yes, Self Balancing                                                                                      |

| Switching Operation                  | Hard                                                                     | ZVS                                                                                                      |

| Frequency (MHz)                      | ~ 0.4                                                                    | ~2                                                                                                       |

| Frequency Variation                  | ± 3.8%                                                                   | ± 0.55%                                                                                                  |

| L                                    | 100 µH                                                                   | 1.5 µH                                                                                                   |

| С                                    | 15 μF (C <sub>o</sub> )                                                  | 4.7 μF (C <sub>o</sub> ) + 1 μF (C <sub>f</sub> )                                                        |

| Peak Power Efficiency<br>(Frequency) | 86% @ V <sub>i</sub> = 50 V,<br>83% @ V <sub>i</sub> = 70 V<br>(0.4 MHz) | 90% @ V <sub>i</sub> = 48 V,<br>86% @ V <sub>i</sub> = 72 V,<br>83% @ V <sub>i</sub> = 100 V,<br>(2 MHz) |

## Summary

- Switched-mode power converters are the most popular DC-DC converters for high-efficiency voltage conversion

- Power topology characteristics with CCM vs DCM operation

- Power loss analysis and efficiency-enhancement techniques

- Passive selection strategy

- Voltage-mode PWM control and its frequency compensation strategy

- Current-mode PWM control and its frequency compensation strategy

- Current sensor design

- Hysteretic control

- Advanced material: Three-level DC-DC converter

- Topology characteristics

- Flying capacitor balancing and gate driver structure

## Related Papers in ISSCC 2018

#### High-voltage DC-DC Converter: Paper 24.1

L. Cong, H. Lee, "A 2MHz 150-to-400V Input Isolated DC-DC Bus Converter with Monolithic Slope-Sensing ZVS Detection Achieving 13ns Turn-on Delay and 1.6W Power Saving," ISSCC 2018.

#### **Low Voltage Ripple Step-Up Converter: Paper 27.5**

S. U. Shin, et. al., "A 95.2% Efficiency Dual-Path DC-DC Step-Up Converter with Continuous Output Current Delivery and Low Voltage Ripple," ISSCC 2018.

# References (1)

- H. Lee and S. Ryu, "An efficiency-enhanced DCM buck regulator with improved switching timing of power transistors," IEEE Transactions on Circuits and Systems-II, vol. 57, no. 3, pp. 238 – 242, Mar. 2010.

- D. Park and H. Lee, "Improvements in light-load efficiency and operation frequency for low-voltage current-mode integrated boost converters," *IEEE Transactions on Circuits and Systems-II*, vol. 61, no. 8, pp. 599 603, Aug. 2014.

- M. D. Mulligan, B. Broach, and T. H. Lee, "A constant-frequency method for improving light-load efficiency in synchronous buck converters," IEEE Power Electronics Letters, pp. 24 - 29, Mar. 2005.

- L. Chen, Y. Liu, and W. H. Ki, "A 10/30MHz wide-duty-cycle-range buck converter with DDA-based Type-III compensator and fast reference-tracking responses for DVS applications," *IEEE International Solid-State Circuits Conference*, Feb. 2014, pp. 84 – 85.

- C. F. Lee and P. K. T. Mok, "A monolithic current-mode CMOS DC-DC converter with on-chip current-sensing technique," *IEEE Journal of Solid-State Circuits*, vol. 39, no. 1, pp. 3 14, Jan. 2004.

- M. Du and H. Lee, "An integrated speed- and accuracy-enhanced CMOS current sensor with dynamically-biased shunt feedback for current-mode buck regulators," *IEEE Transactions on Circuits and Systems-I*, vol. 57, no. 10, pp. 2804 – 2814, Oct. 2010.

# References (2)

- M. Du, H. Lee, and J. Liu, "A 5-MHz 91% peak-power-efficiency buck regulator with auto-selectable peak- and valley-current control," *IEEE Journal of Solid-State Circuits*, vol. 46, no. 8, pp. 1928 1939, Aug. 2011.

- D. Ma, et. al., "Single-inductor multiple-output switching converters with time-multiplexing control in discontinuous conduction mode," *IEEE Journal of Solid-State Circuits*, vol. 38, no. 1, pp. 89 – 100, Jan. 2003.

- □ F. Su and W. H. Ki, "Digitally assisted quasi-V<sup>2</sup> hysteretic buck converter with fixed frequency and without using large-ESR capacitor," *IEEE International Solid-State Circuits Conference*, Feb. 2009, pp. 446 447.

- Z. Liu, L. Cong, and H. Lee, "Design of on-chip gate drivers with power-efficient high-speed level shifting and dynamic timing control for high-voltage synchronous switching power converters," *IEEE Journal of Solid-State Circuits*, vol. 50, no. 6, pp. 1463 – 1477, Jun. 2015.

- Z. Liu and H. Lee, "A 26W 97%-efficiency fast-settling dimmable LED driver with dual-nMOSsensing based glitch-tolerant synchronous current control for high-brightness solid-state lighting applications," *IEEE Journal of Solid-State Circuits*, vol. 50, no. 9, pp. 2174 – 2187, Sep. 2015.

- □ S. H. Lee, et. al., "A 0.518mm<sup>2</sup> quasi-current-mode hysteretic buck DC-DC converter with 3µs transient response in 0.35µm BCDMOS," *IEEE International Solid-State Circuits Conference*, Feb. 2015, pp. 214 215.

# References (3)

- L. Cong and H. Lee, "A 110 250V 2MHz isolated DC-DC converter with integrated high-speed synchronous gate drive," IEEE Energy Conversion Congress and Exposition, Sep. 2015, pp. 1479 – 1484.

- □ J. Xue, L. Cong, and H. Lee, "A 100-V 2-MHz isolated QSW-ZVS three-level DC-DC converter with on-chip dynamic dead-time controlled synchronous gate driver for eGaN power FETs," *IEEE Applied Power Electronics Conference*, Mar. 2015, pp. 451 454.

- □ J. Xue and H. Lee, "A 2MHz 12 100V 90%-efficiency self-balancing ZVS three-level DC-DC regulator with constant-frequency AOT V<sup>2</sup> control and 5ns ZVS turn-on delay," *IEEE International Solid-State Circuits Conference*, Feb. 2016, pp. 226 227.

- J. Xue and H. Lee, "A 2MHz 12V 100V 90%-efficiency self-balancing ZVS reconfigurable threelevel DC-DC regulator with constant-frequency adaptive-on-time V<sup>2</sup> control and nanosecond-scale ZVS turn-on delay," *IEEE Journal of Solid-State Circuits*, vol. 51, no. 12, pp. 2854 – 2866, Dec. 2016.

- H. Lee, Z. Hua, and X. Zhang, "A reconfigurable 2x/2.5x/3x/4x SC DC-DC regulator with fixed ontime control for transcutaneous power transmission," *IEEE Transactions on Very Large Scale Integration Systems*, vol. 23, no. 4, pp. 712 – 722, Apr. 2015.